За каких-то три года компания TSMC незаметно стала крупнейшим в мире упаковщиком чипов объёмной (3D) компоновки. Как сообщает тайваньский интернет-ресурс DigiTimes, в области 2.5D/3D-упаковки чипов TSMC обладает возможностями обрабатывать до 200 тыс. подложек в месяц. Для сравнения, лидирующие на рынке упаковки чипов компании Advanced Semiconductor Engineering (ASE) и Amkor Technology могут ежемесячно упаковывать в 2.5D/3D-упаковку кристаллы с 20–30 тыс. пластин каждая, а компания Siliconware Precision Industries (SPIL) — 100–120 тыс. пластин. Ради справедливости уточним, все перечисленные компании (кроме TSMC) имеют куда большие возможности для упаковки обычных планарных или одиночных кристаллов, куда TSMC вход заказан.

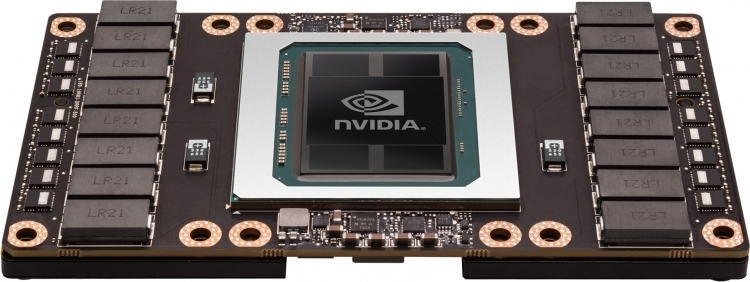

NVIDIA Tesla P100 (пример упаковки TSMC CoWoS, GPU и HBM)

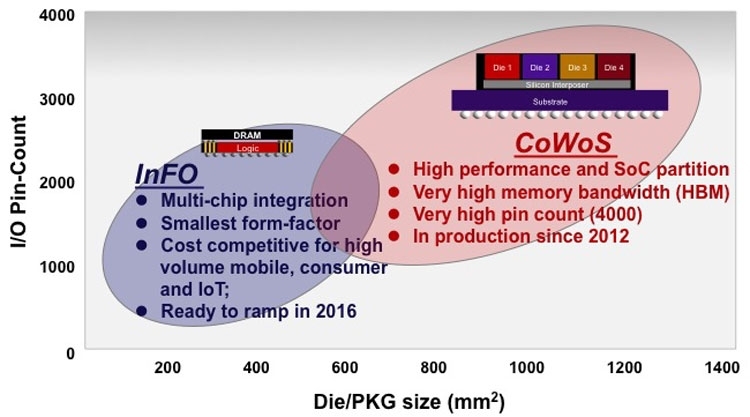

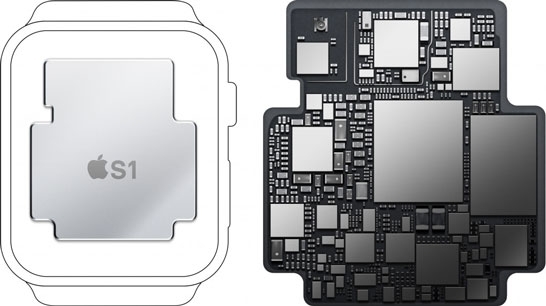

История самостоятельной 2.5D/3D-упаковки TSMC началась с покупки в 2014 году тайваньского завода компании Qualcomm по выпуску дисплеев Mirasol на MEMS-ячейках. Тайваньский производитель превратил завод Qualcomm в фабрику по передовой упаковке чипов. Внедрённый на предприятии метод упаковки InFO-WLP (integrated fan-out wafer-level packaging) помог TSMC выиграть заказы на выпуск часов Apple Watch и 10-нм SoC Apple. В настоящий момент на предприятии в основном применяется метод упаковки CoWoS (chip on wafer on substrate), с помощью которого, например, TSMC выпускает GPU NVIDIA Volta с памятью HBM на общей подложке. Но это всё упаковка 2.5D, которая использует тот или иной субстрат (мост, подложку).

2.5D упаковка TSMC: InFO и CoWoS

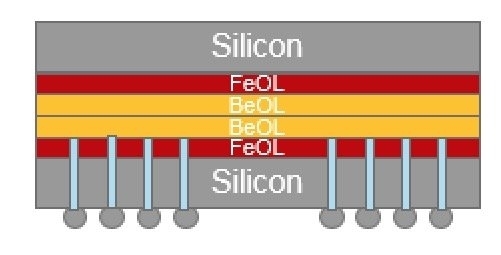

Настоящая 3D-упаковка начнётся с освоения технологии WoW (wafer-on-wafer). Это прямая состыковка кристаллов либо со стороны контактной группы, либо с лицевой стороны (со стороны расположения элементов). Сообщатся даже о первом клиенте на эту технологию, которым якобы стала компания HiSilicon (подразделение Huawei).

Пример упаковки Wafer on Wafer (Cadence)

Сообщается, что для упаковки WoW и более прогрессивных методов производства чипов компания TSMC собирается строить на севере Тайваня новый завод. В компании TSMC не подтвердили эту информацию, но знакомые с работой правительственного агентства по контролю за окружающей средой источники раскрыли, что Environmental Protection Administration (EPA) начала оценку влияния возможного завода на среду вблизи города Чунань в провинции Мяоли.

Apple S1 для «умных» часов Apple (упаковка типа SiP)

Объёмная упаковка чипов представляется ключевой технологией для продления действия закона Мура. Пусть в видоизменённой форме, но этот закон продолжит работать. Это означает дальнейший прогресс в деле выпуска более совершенных полупроводниковых решений, а для компании TSMC самостоятельное участие в процессе прогрессивной упаковки чипов станет гарантией успешного будущего.

Ноябрь 15th, 2024

Ноябрь 15th, 2024  raven000

raven000  Опубликовано в рубрике

Опубликовано в рубрике